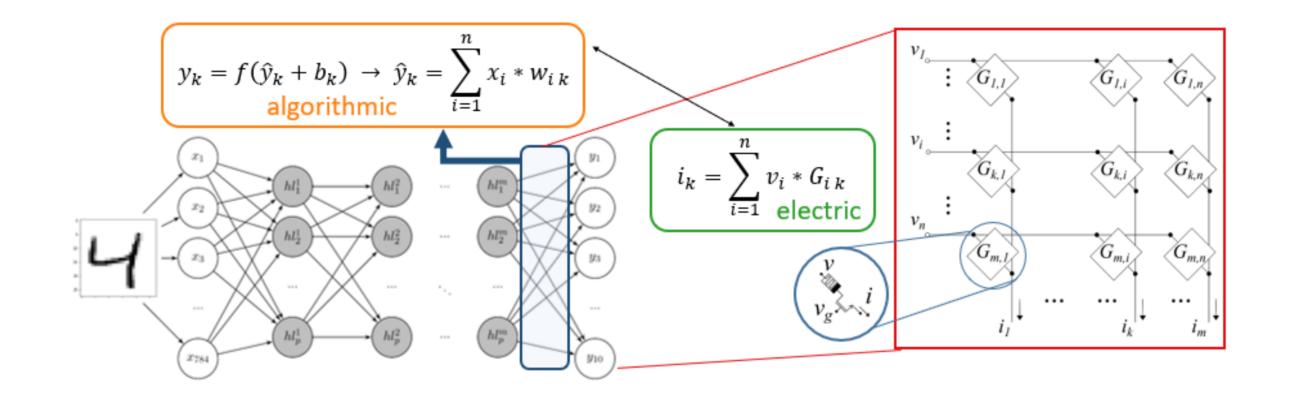

New technology approaches for neuromorphic computing Memristor applications: In-memory computing in crossbar architecture

## In-Memory Computing 1

Most of the power consumption in AI accelerators is due to the well-known memory wall problem.

**Solution**: In-memory computing; the data is computed where it is stored.

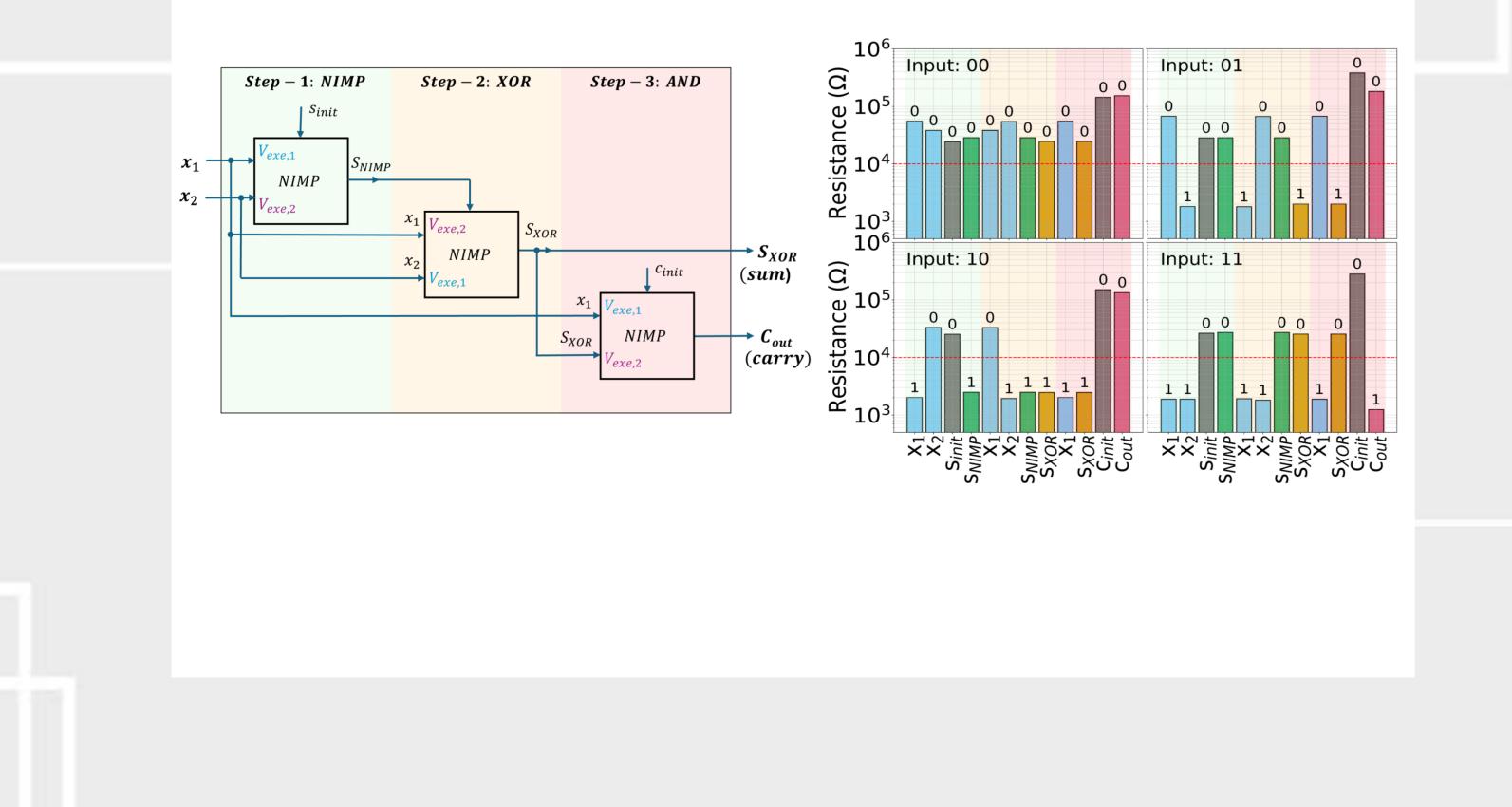

Half-adder Implementation with RRAMs 3

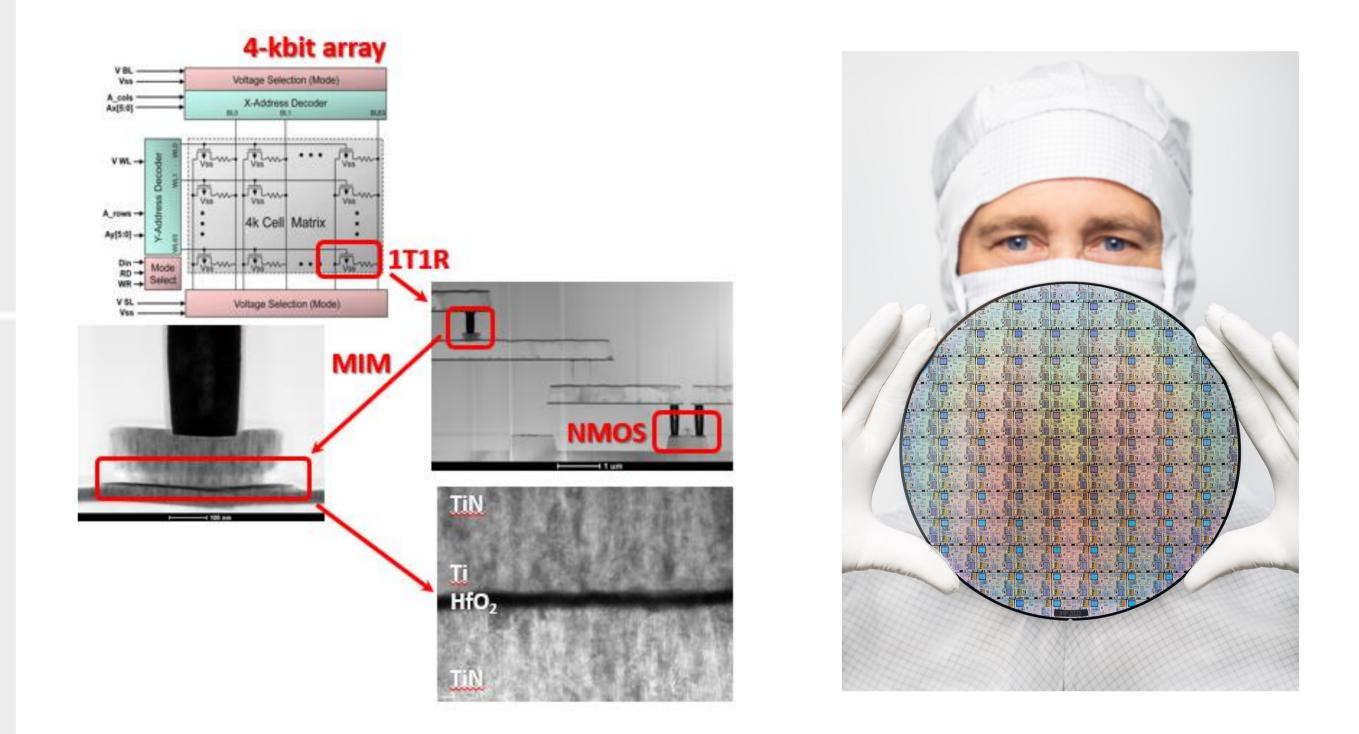

## 200 mm CMOS RRAM Technology 2

CMOS integrated 4 Kbit test array with peripheral drive electronics, developed in the 130 nm technology node of the IHP.

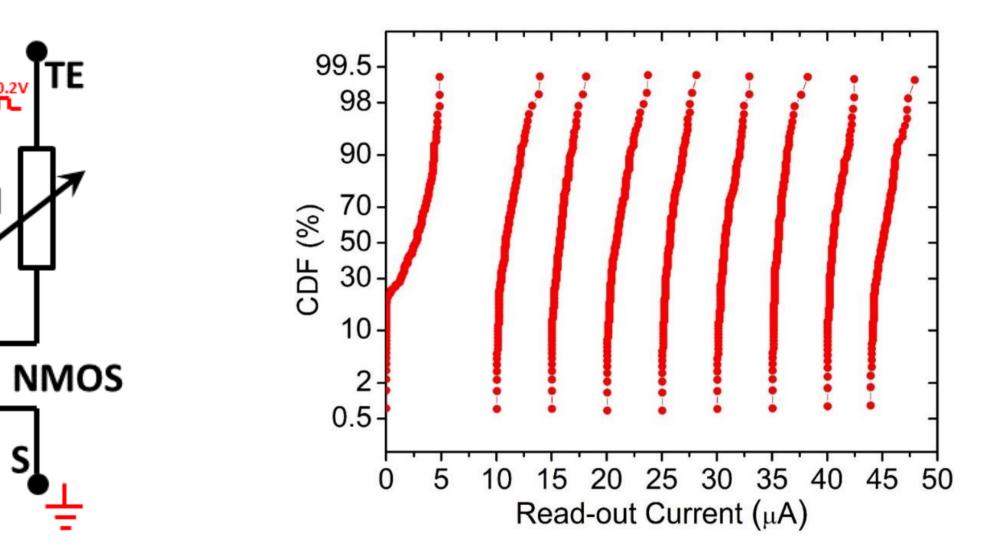

## Verified algorithms for programming multiple conductive states

Integration of TaOx/Ta-RRAM on a CMOS substrate and realization of a half adder in 31x16 crossbar array using inmemory computing.

IGVVA

0.5V 0.6V

ΜΙΜ

## Outlook 4

1.7V

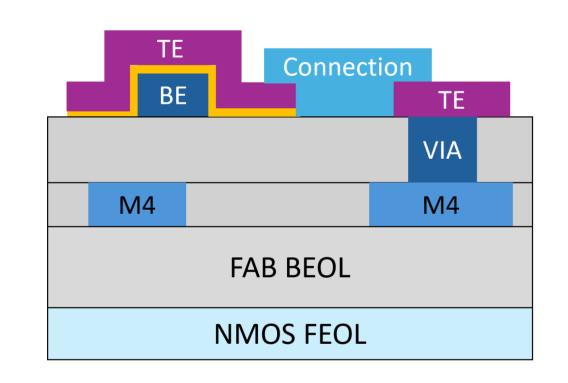

Making a process line for next-generation neuromorphic systems co-integrated with CMOS platform available:

Extension of the existing IHP process environment for the targeted expansion of the structuring capabilities of the integrated **RRAM** devices.

Extension of the existing 200 mm silicon cluster by the components metal PVD, metal oxide PVD and handler, for the deposition of analog switchable RRAM devices.

SPONSORED BY THE

Federal Ministry

of Education

and Research